5

13

2015

DA-300USBのデータ信号フォーマット

DA-300USB内部のデータ信号のフォーマットを調べてみた

DA-300USBを自分でカスタマイズするために内部構造を調べてみたが、デジタル処理系基板からDAC部のメイン基板に渡されるオーディオデータ信号の受け渡し方法般的なI2Sデータ信号の形式ではないようなので、デジタル信号系の扱いを少しだけ探ってみた.

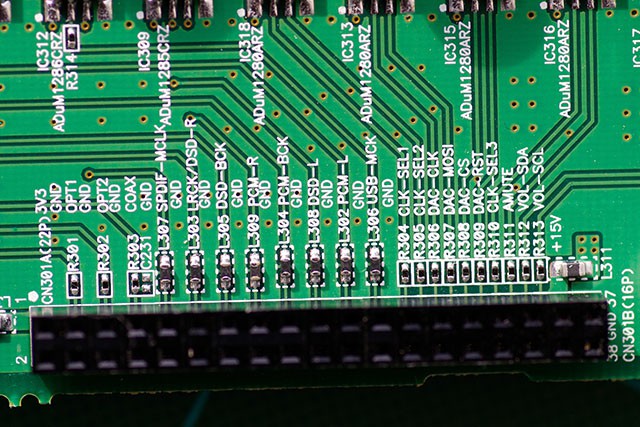

メイン基板のコネクタ部のシルク印刷に記されているデータ信号名

先ず、DAC部のメイン基板のコネクタ部のシルク印刷に記されているデータ信号名を拾ってみると、

・Pin#11 LRCK/DSD-R PCM信号のLRCK信号(DSDのRチャネル信号と兼用)

・Pin#13 DSD-BCK DSDのビットクロック信号

・Pin#15 PCM-R PCMのRチャネル信号

・Pin#17 PCM-BCK PCM信号のビットクロック信号

・Pin#19 DSD-L DSDのLチャネル信号

・Pin#21 PCM-L PCMのLチャネル信号

・Pin#23 USB-MCK DACへのマスタークロック信号(USB入力系)

となっている.これらのPCM系信号のうち、PCM-L, PCM-Rが一般的なPCM形式のオーディオデータ信号のようだが、通常のオーディオシリアルデータ信号DATA(SDATA)とはどうも信号の扱いが異なっているみたいだ.実は以前オシロスコープでLRCKやPCM-BCKの波形を観察した際に、一般的なI2S信号とは大部様子が異なっていた.44.1KHzのPCMデータを入力した際に、LRCKのクロック周波数が714KHzとなっており、8倍アップサンプリングされた352.8KHzの倍以上の数値だったので不思議に思っていた.

これらの信号ラインが、DACチップのどの端子につながっているのかを調べてみた結果、一般的なPCMデジタル信号の入力方法とは異なる方法でつないでいるようなので、DACチップのデータシートをきちんと調べてみると、DACチップ内部の8倍オーバーサンプリングや内部デジタルフィルタを使わずに、外部のデジタルフィルタを使う、”External Digital Filter” モードを使用していることが判明した.

DA-300USBの最大の特徴である、AL32デジタル信号ビット補完処理機能と独自のデジタルフィルタリングモードを売りにしているので、当然DACチップの8倍オーバーサンプリングデジタルフィルター機能はバイパスすることになる.従ってDACチップの使い方も一般的なPCMデータ処理系とは異なっている.

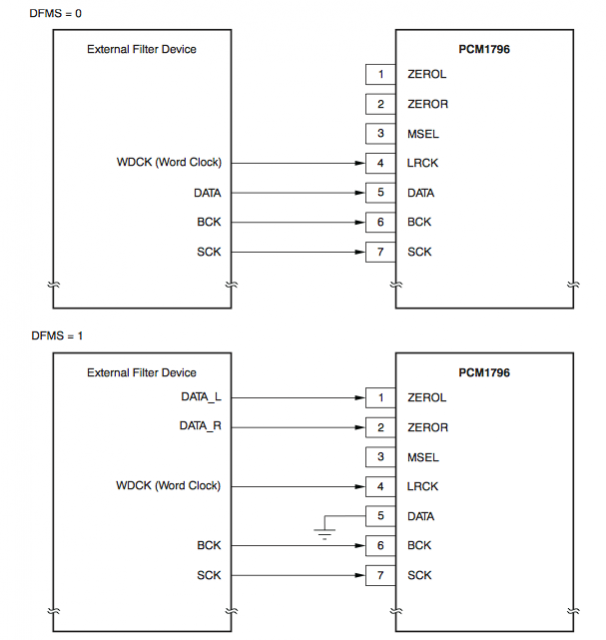

Connection Diagram for External Digital Filter (Internal DF Bypass Mode)

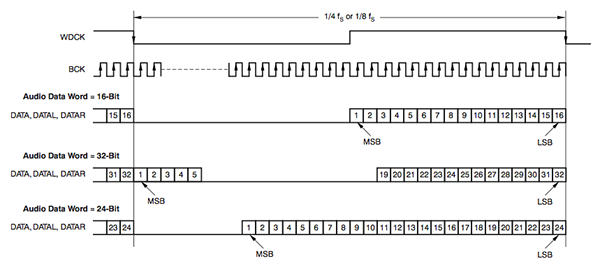

Audio Data Input Format for External Digital Filter

上図はPCM1795のデータシートに記載されている外部デジタルフィルターモード時の接続図だが、DA-300USBでは左右のチャネルを別々に入力する(DFMS=1)方式を採用している.図ではPCM1976と記載されているが、PCM1972,1975,1976はピンコンパチブルなのでPCM1975でも同じピン配置だ.

データシートの外部デジタルフィルターモードの解説によると、

• LRCK (pin 4): WDCK as word clock input

• BCK (pin 6): Bit clock for audio data

• DATA (pin 5): Monaural audio data input when the DFMS bit is not set to 1

• ZEROL (pin 1): DATAL as left channel audio data input when the DFMS bit is set to 1

• ZEROR (pin 2): DATAR as right channel audio data input when the DFMS bit is set to 1

”The word clock (WDCK) signal must be operated at 8 times or 4 times the desired sampling frequency, fS.”

ワードクロック(WDCK) は サンプリング周波数の4倍か8倍に設定する必要がある.(※ 何故か16倍の説明が抜けている)

”The PCM1795 device in the external digital filter interface mode supports right-justified audio formats including 16-bit, 24-bit, and 32-bit audio data. ”

外部デジタルフィルターモードでは、right-justifiedフォーマットの16,24,32ビットモードをサポートしている.

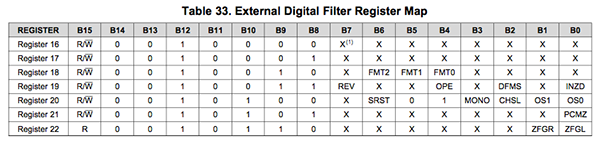

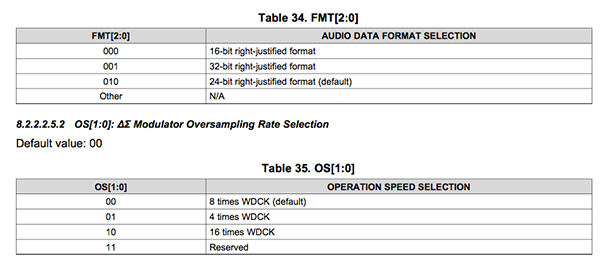

PCM1795のRegister Map

データフォーマットとワードクロック(WDCK) の設定ビット

DACへのPCMデータ入力信号とSPI制御信号を覗いてみた

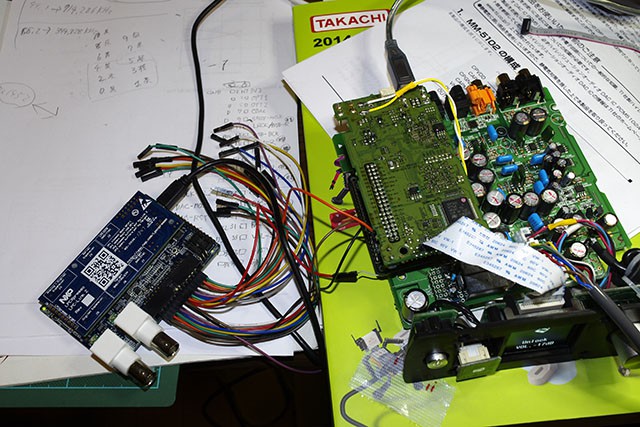

DA-300USBのUSBデジタル信号処理基板からDACメインボードにどのような信号が渡されているのか、簡易ロジックアナライザを用いて実際にデータをキャプチャしてみた.

簡易ロジックアナライザとして利用可能な “LabTool” でデジタル信号をキャプチャする

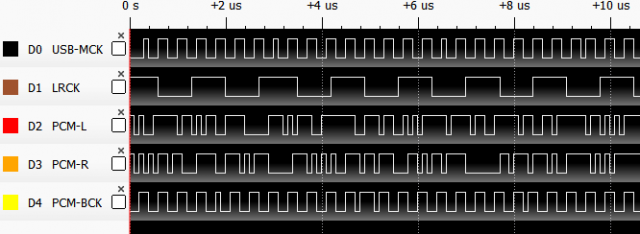

PCM 44.1KHz Mode時のDACへのPCM入力信号

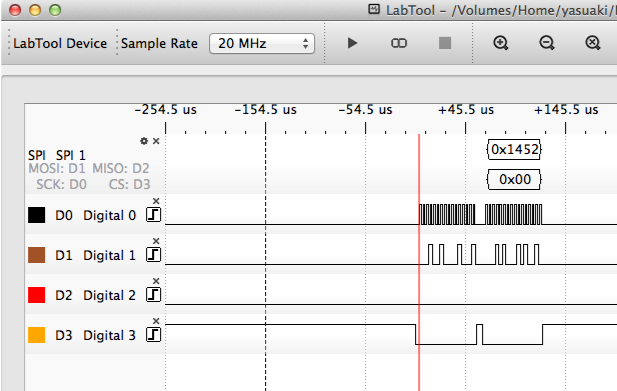

電源投入後のDACチップ初期化を行っている[Register #20: SRST:1 DSD:0 DFTH:1 MONO:0 CHSL:0 OS1:1 OS0:0]

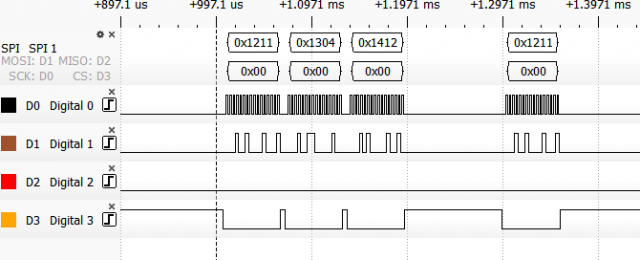

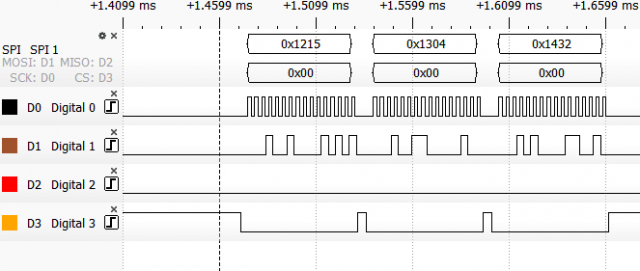

PCM 44.1KHz モード時のSPI制御信号

DSD128(5.6MHz) モード時のSPI制御信号

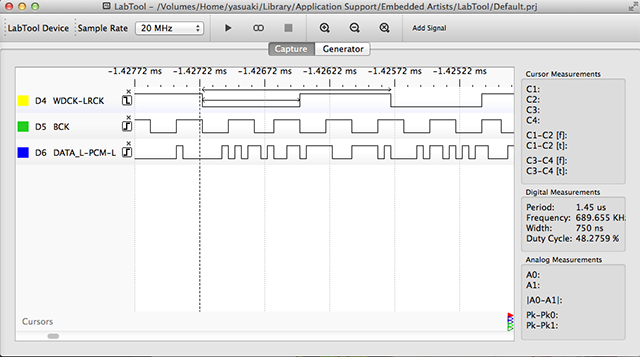

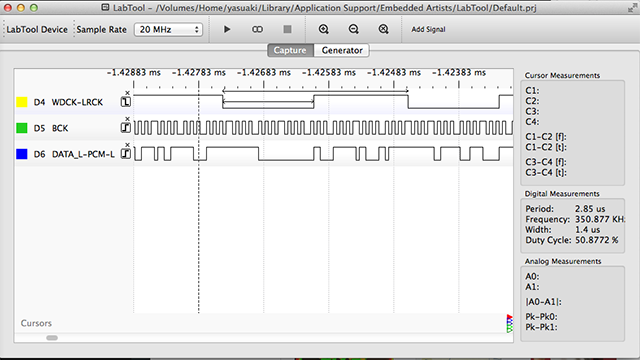

PCM 44.1KHz入力モード時の WDCK,BCK信号(WDCK: 705.6KHz x 16fs)

PCM 48.0KHz入力モード時の WDCK,BCK信号(WDCK: 768KHz x 16fs)

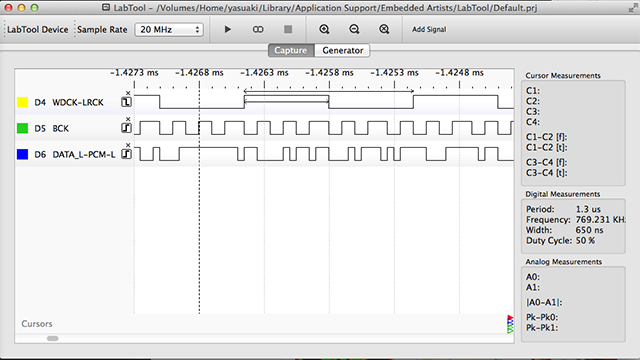

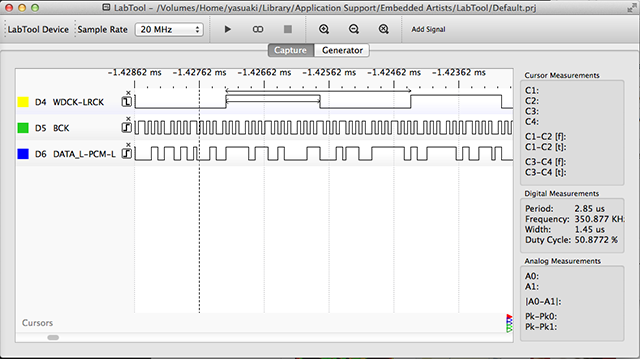

PCM 88.2KHz入力モード時の WDCK,BCK信号(WDCK: 352.8KHz x 4fs)

PCM 176.4KHz入力モード時の WDCK,BCK信号(WDCK: 352.8KHz x 2fs)

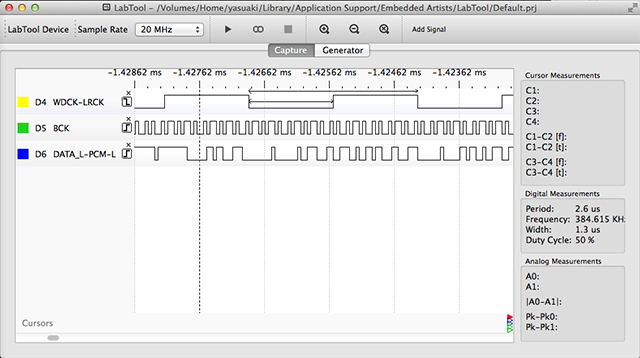

PCM 192.0KHz入力モード時の WDCK,BCK信号(WDCK: 384.0KHz x 2fs)

PCMデータ入力時のWDCKの周波数をロジックアナライザの周期測定データで調べてみると、入力信号のサンプリング周波数が44.1KHz/48.0KHz 時には、WDCKの周波数はサンプリング周波数 fs の16倍(705.6KHz/768KHz)となっている.同じく、88.2KHz/96KHzの場合は fs の4倍(352.8.6KHz/384KHz)、176.4KHz/192KHzの場合は fs の2倍(352.8.6KHz/384KHz)に設定されている.

DACチップをPCM1792に交換する事は可能か?

今回、内部のデジタル信号のハンドリングを調べてみて、PCM1795とピン&モードコントロールコンパチな筈のPCM1792にはそのままでは置き換える事ができない事が判明した.問題となるのはDA-300USBが使用している、外部デジタルフィルターモードが “right-justified” を使用しており、データフォーマットの設定ビット(コントロールレジスタ #18: FMT[2:0] bits )の値 “001” が PCM1795では 32bits-right-justified、 PCM1792では 20bits-right-justified になっているので、PCM1792チップの場合は 32bit長データのLSB側20bitsが採用されてしまう事になる.このフォーマットのコード設計に関してはメーカー側の設計がちょっとずさんというか間抜けな感じがする.同じシリーズのDACチップでピン互換を売りにしているのなら、少なくともフォーマットのコードはシリーズ間で共通にするのが普通だと思うが、何故後発のPCM1795での32bitモード時のフォーマットコードを過去のコードとぶつかる設計をしたのだろうか.

オーディオデータのフォーマットとデータビット長の問題があるので、DA-300USBの場合はピン互換なPCM1792に単純に置き換える事はできない.32bits right-justifiedデータを24bits right-justifiedに変換するには、74HC594などの汎用的なシフトレジスタチップを間に噛ませばフォーマットの変換は何とかなりそうだが、DAC側のコントロールレジスタ#18のFMTの値を24bit用の “010” に変更するのはちょっと難しそうだ.PCM1795用のSPI制御コードを受け取ってターゲット用のDACチップのSPIあるいはI2C制御コードに変換(仲介かな?)するインタプリターのような仕組みが必要になるだろう.PICやNXPなどのコントローラチップで処理系を作らなければならないのでかなり厄介な事になりそうだ.

DA-300USBのデジタル処理系のDAC制御コードはPCM1795チップに依存しているので、そのままでは汎用的な高性能USB-IFとしての利用は難しい.